Document: ETG.2200 G D V3.2.2

SECTION I – EtherCAT SubDevice introduction and implementation procedure

SECTION II - ESC overview and EtherCAT development products

**SECTION III – EtherCAT P introduction and implementation**

SECTION IV - Safety over EtherCAT introduction and implementation

Created by: EtherCAT Technology Group Contact: techinfo@ethercat.org

Date: 21.05.2025 Version V3.2.2

## **LEGAL NOTICE**

## **Trademarks and Patents**

EtherCAT®, Safety over EtherCAT® and EtherCAT P® are registered trademark and patented technology, licensed by Beckhoff Automation GmbH & Co. KG, Germany. Other designations used in this publication may be trademarks whose use by third parties for their own purposes could violate the rights of the owners.

#### Disclaimer

The documentation has been prepared with care. The technology described is, however, constantly under development. For that reason, the documentation is not in every case checked for consistency with performance data, standards or other characteristics. In the event that it contains technical or editorial errors, we retain the right to make alterations at any time and without warning. No claims for the modification of products that have already been supplied may be made based on the data, diagrams and descriptions in this documentation.

#### Copyright

© EtherCAT Technology Group, 2025.

The reproduction, distribution and utilization of this document as well as the communication of its contents to others without express authorization is prohibited. Offenders will be held liable for the payment of damages. All rights reserved in the event of the grant of a patent, utility model or design.

#### DOCUMENT ORGANIZATION

This document provides help for implementing an EtherCAT© SubDevice from a generic and a practical point of view. It answers the following questions:

- How is the EtherCAT SubDevice architecture?

- What steps are helpful to implement an EtherCAT SubDevice?

- Which documents are available?

- What kinds of EtherCAT development components are available? What are the differences?

- Is EtherCAT training and implementation support available?

- Why attend an EtherCAT Plug Fest?

- How to obtain conformance for EtherCAT devices?

There are many possibilities for how EtherCAT SubDevice implementation can be realized. However, the way described in this document has proved to lead to a fast EtherCAT SubDevice implementation. The document is organized in four sections:

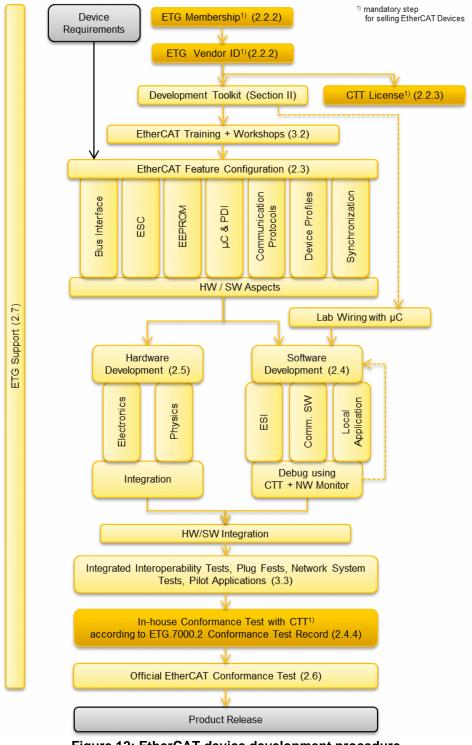

SECTION I – EtherCAT SubDevice introduction and implementation procedure provides principal aspects of an EtherCAT SubDevice implementation and provides further information including a list of useful tools and available trainings.

SECTION II – ESC overview and EtherCAT development products provides device specific descriptions for further implementation aspects and an overview of available evaluation boards and EtherCAT SubDevice Controllers (ESCs).

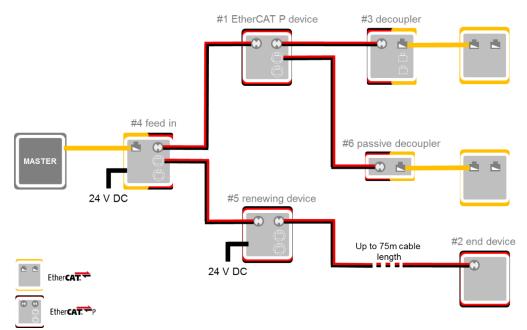

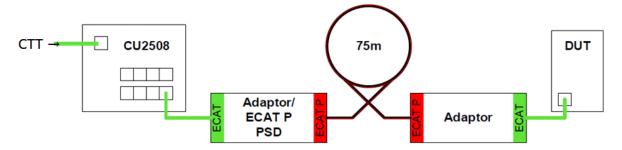

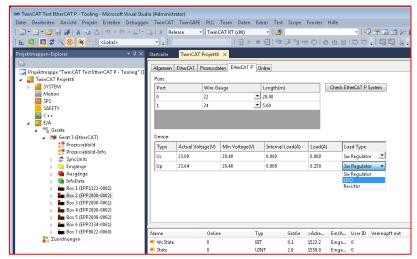

SECTION III – EtherCAT P introduction and implementation provides implementation topics as well as testing conditions for the EtherCAT enhancement "EtherCAT P".

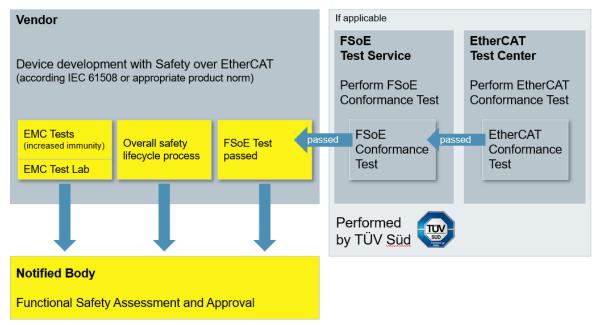

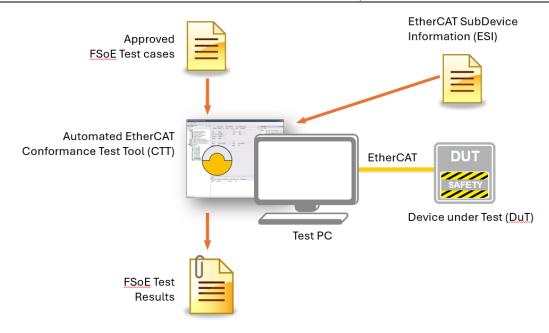

SECTION IV – Safety over EtherCAT introduction and implementation provides detailed information about implementing Safety over EtherCAT, references to related Safety over EtherCAT specifications and documents, as well as licensing and conformance testing.

# **ABBREVIATIONS**

| Abbreviations | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| μC / MCU      | A <b>m</b> icro <b>c</b> ontroller (MCU for microcontroller unit) is a small computer on a single integrated circuit. A microcontroller contains one or more CPUs (processor cores) along with memory and programmable input/output peripherals. Program memory in the form of ferroelectric RAM, NOR flash or OTP ROM is also often included on chip, as well as a small amount of RAM. Microcontrollers are designed for embedded applications, in contrast to the microprocessors used in personal computers or other general purpose applications consisting of various discrete chips. (www.wikipedia.org) |

| ADS           | The Automation Device Specification describes a device- and fieldbus-independent interface. This interface got designed by Beckhoff, and is - including the protocol - in detail documented. The ADS components get installed together with TwinCAT 3. For integration into own applications and tools there are ADS components (C/C++, .NET) available from Beckhoff. (Beckhoff Information System)                                                                                                                                                                                                            |

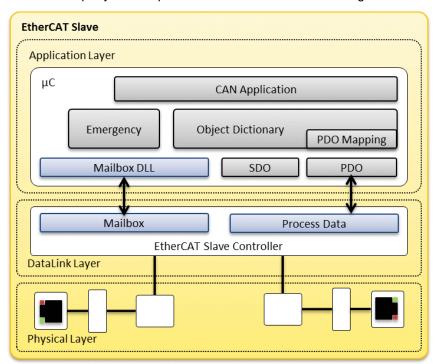

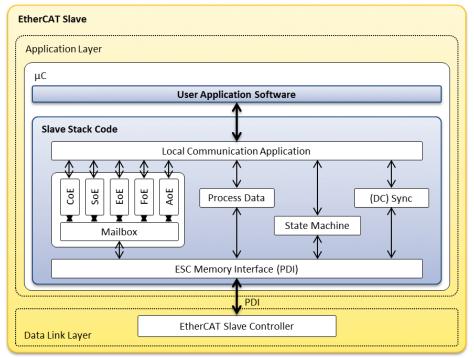

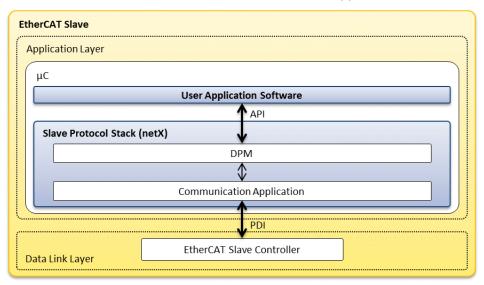

| AL            | The Application Layer describes the highest layer of the EtherCAT SubDevice stack which includes the EtherCAT State Machine, error handling, mailbox protocol handling, SubDevice application                                                                                                                                                                                                                                                                                                                                                                                                                   |

| AoE           | <b>A</b> DS <b>o</b> ver <b>E</b> therCAT (AoE) is a standard, client-server mailbox application protocol defined by the EtherCAT specification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| API           | In computer programming, an <b>A</b> plication <b>P</b> rogramming <b>I</b> nterface is a set of subroutine definitions, communication protocols, and tools for building software. In general terms, it is a set of clearly defined methods of communication among various components. (www.wikipedia.org)                                                                                                                                                                                                                                                                                                      |

| ASIC          | An <b>A</b> pplication- <b>S</b> pecific Integrated Circuit is an integrated circuit (IC) customized for a particular use, rather than intended for general-purpose use. (www.wikipedia.org)                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CAN           | A <b>C</b> ontroller <b>A</b> rea <b>N</b> etwork (CAN bus) is a robust vehicle bus standard designed to allow microcontrollers and devices to communicate with each other in applications without a host computer. It is a message-based protocol, designed originally for multiplex electrical wiring within automobiles to save on copper, but is also be used in many other contexts. (www.wikipedia.org)                                                                                                                                                                                                   |

| CiA           | <b>C</b> AN <b>i</b> n <b>A</b> utomation is the international users' and manufacturers' organization that develops and supports CAN-based higher-layer protocols. (www.wikipedia.org)                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CoE           | With the <b>C</b> AN® application protocol <b>o</b> ver <b>E</b> therCAT protocol, EtherCAT provides the same communication mechanisms as in CANopen®-Standard EN 50325-4: Object Dictionary, PDO Mapping (Process Data Objects) and SDO (Service Data Objects) – even the network management is similar. This makes it possible to implement EtherCAT with minimal effort in devices that were previously outfitted with CANopen, and large portions of the CANopen Firmware are even reusable. (www.ethercat.org)                                                                                             |

| CPU           | A Central Processing Unit, also called a central processor or main processor, is the electronic circuitry within a computer that carries out the instructions of a computer program by performing the basic arithmetic, logic, controlling, and input/output (I/O) operations specified by the instructions. (www.wikipedia.org)                                                                                                                                                                                                                                                                                |

| DC            | Distributed Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DLL           | The <b>D</b> ata <b>L</b> ink <b>L</b> ayer is the second layer of the seven-layer OSI model of computer networking. This layer is the protocol layer that transfers data between adjacent network nodes in a wide area network (WAN) or between nodes on the same local area network (LAN) segment. The data link layer provides the functional and procedural means to transfer data between network entities and might provide the means to detect and possibly correct errors that may occur in the physical layer. (www.wikipedia.org)                                                                     |

| DPRAM         | Dual Ported Random Access Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DuT           | A <b>D</b> evice <b>u</b> nder <b>T</b> est is a manufactured product undergoing testing, either at first manufacture or later during its life cycle as part of ongoing functional testing and calibration checks. This can include a test after repair to establish that the product is performing in accordance with the original product specification.                                                                                                                                                                                                                                                      |

| EEPROM        | An Electrically Erasable Programmable Read-Only Memory is a type of non-volatile memory used in computers, integrated in microcontrollers for smart cards and remote keyless systems, and other electronic devices to store relatively small amounts of data but allowing individual bytes to be erased and reprogrammed. (www.wikipedia.de)                                                                                                                                                                                                                                                                    |

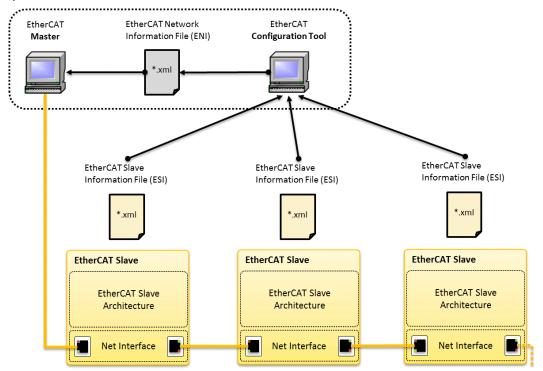

| ENI           | The <b>E</b> therCAT <b>N</b> etwork <b>I</b> nformation represents the standardized, XML-based description of an EtherCAT network. It provides a manufacturer-independent way for configuration tools to generate and provide the network configuration to MainDevices. (www.ethercat.org)                                                                                                                                                                                                                                                                                                                     |

| EoE           | Ethernet Over EtherCAT allows one to use a Standard Ethernet device like a printer, camera or PC within an EtherCAT network. There is no restriction on the type of Ethernet device that can be connected. The frames are tunneled by the EtherCAT MainDevice via the EtherCAT protocol. The EtherCAT networks is fully transparent for the Ethernet device, and the real-time characteristics are not impaired. (www.ethercat.org)                                                                                                                                                                             |

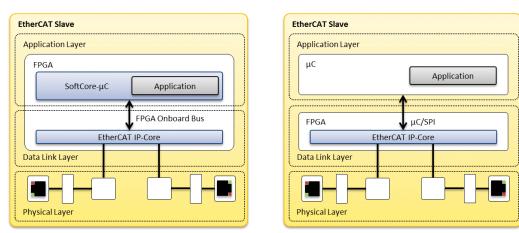

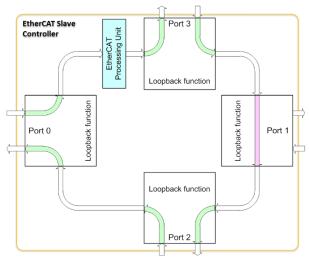

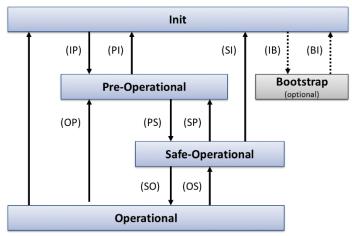

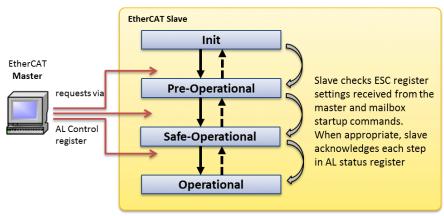

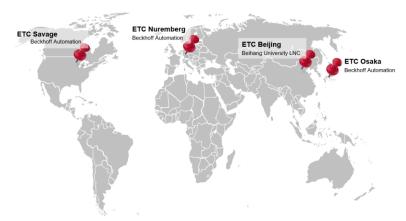

| The EtherCAT Processing Unit is the logical core of an EtherCAT SubDevice Controller. It con registers, memories and data processing elements. A frame always comes from port A before p through the EtherCAT Processing Unit. It receives, analyzes and processes from port A before p through the EtherCAT SubDevice Controller processes the EtherCAT frames on the fly in hardware. It implementation can be as an ASIC device, as IP Core for FPGAs, as system on a chip (SoC) or integrated as native EtherCAT interface on an microcontroller or CPU. There is a long list of ES different types and vendors. (Knowledge Base)  ESI  The EtherCAT SubDevice Information file is a XML based file that comes with an EtherCAT SubDevice and contains the complete description of its network accessible properties, such as manufacturer and product information, Process Data, their mapping options, supported Mailbox application protocols including optional features, as well as the supported modes of Synchroniza (www.ethercat.org)  ESM  The state of the EtherCAT SubDevice is controlled via the EtherCAT State Machine. Depending the state, different functions are accessible or executable in the EtherCAT SubDevice. Specific commands must be sent by the EtherCAT MainDevice to the device in each state, particularly of the bootup of the SubDevice. A distinction is made between the following states: init, pre-operational state (Beckhoff Infosys/Anpassung: CH)  ETC  The official EtherCAT Test Center in Eurodpe, Asia and North America are accredited by the Eard perform the official EtherCAT Conformance Test. (ETG Brochure 11/2018)  ETG  The EtherCAT Technology Group is a global organization in which OEM, End Users and Tech Providers join forces to support and promote the further technology development. (www.etherce EtherCAT  The EtherCat Technology Group is a standardized in IEC 61158 and is suitable for both hard are real-time computing requirements in automation technology. (www.wikipedia.org)  EtherCAT Device  Beckhoff Automation. The protocol is stand | eassing c's c's construction cation. construction during |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

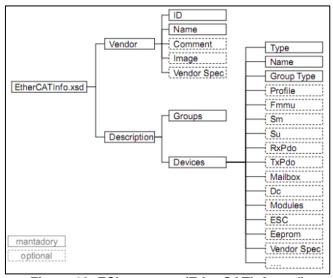

| implementation can be as an ASIC device, as IP Core for FPGAs, as system on a chip (SoC) or integrated as native EtherCAT interface on an microcontroller or CPU. There is a long list of ES different types and vendors. (Knowledge Base)  The EtherCAT SubDevice Information file is a XML based file that comes with an EtherCAT SubDevice and contains the complete description of its network accessible properties, such as manufacturer and product information, Process Data, their mapping options, supported Mailbox application protocols including optional features, as well as the supported modes of Synchroniza (www.ethercat.org)  The state of the EtherCAT SubDevice is controlled via the EtherCAT SubDevice. Specific commands must be sent by the EtherCAT MainDevice to the device in each state, particularly of the bootup of the SubDevice. A distinction is made between the following states: init, pre-operat safe-operational and operational, boot. The regular state of each EtherCAT SubDevice after bothe operational state (Beckhoff Infosys/Anpassung: CH)  ETC  The official EtherCAT Test Center in Eurodpe, Asia and North America are accredited by the Eand perform the official EtherCAT Conformance Test. (ETG Brochure 11/2018)  ETG  The EtherCAT Technology Group is a global organization in which OEM, End Users and Tech Providers join forces to support and promote the further technology development. (www.ethercate)  EtherCAT  The Ether for Control Automation Technology is an Ethernet-based fieldbus system, inverse Beckhoff Automation. The protocol is standardized in IEC 61158 and is suitable for both hard are real-time computing requirements in automation technology. (www.wikipedia.org)  EtherCAT Device  FCS  A Frame Check Sequence refers to an error-detecting code added to a frame in a communicate protocol. (www.wikipedia.org)  The Fieldbus Memory Management Unit belongs to the DLL and can be found in each I/O terr FMMUs are used to map logical addresses bitwise or bytewise to physical addresses of the Eth SubDevice Controller. ( | r<br>CS of<br>ation.<br>ng upon                          |

| SubDevice and contains the complete description of its network accessible properties, such as manufacturer and product information, Process Data, their mapping options, supported Mailbox application protocols including optional features, as well as the supported modes of Synchronizz (www.ethercat.org)  ESM  The state of the EtherCAT SubDevice is controlled via the EtherCAT State Machine. Dependir the state, different functions are accessible or executable in the EtherCAT SubDevice. Specific commands must be sent by the EtherCAT MainDevice to the device in each state, particularly of the bootup of the SubDevice. A distinction is made between the following states: init, pre-operat safe-operational and operational, boot. The regular state of each EtherCAT SubDevice after both the operational state (Beckhoff Infosys/Anpassung: CH)  ETC  The official EtherCAT Test Center in Eurodpe, Asia and North America are accredited by the E and perform the official EtherCAT Conformance Test. (ETG Brochure 11/2018)  ETG  The EtherCAT Technology Group is a global organization in which OEM, End Users and Tech Providers join forces to support and promote the further technology development. (www.ethercat The Ethernet for Control Automation Technology is an Ethernet-based fieldbus system, invertigation and the suitable for both hard are real-time computing requirements in automation technology. (www.wikipedia.org)  EtherCAT Device  FCS  A Frame Check Sequence refers to an error-detecting code added to a frame in a communicate protocol. (www.wikipedia.org)  The Fieldbus Memory Management Unit belongs to the DLL and can be found in each I/O terr FMMUs are used to map logical addresses bitwise or bytewise to physical addresses of the Eth SubDevice Controller. (Beckhoff Infosys)  FoE  File Access over EtherCAT is a mailbox application protocol generally intended to transfer file an EtherCAT network in both directions, and as such it can be used in any state where the maill                                                                   | ation.  ng upon  during                                  |

| the state, different functions are accessible or executable in the EtherCAT SubDevice. Specific commands must be sent by the EtherCAT MainDevice to the device in each state, particularly of the bootup of the SubDevice. A distinction is made between the following states: init, pre-operat safe-operational and operational, boot. The regular state of each EtherCAT SubDevice after boot the operational state (Beckhoff Infosys/Anpassung: CH)  ETC The official EtherCAT Test Center in Eurodpe, Asia and North America are accredited by the E and perform the official EtherCAT Conformance Test. (ETG Brochure 11/2018)  ETG The EtherCAT Technology Group is a global organization in which OEM, End Users and Tech Providers join forces to support and promote the further technology development. (www.ethercatherCAT Tether for Control Automation Technology is an Ethernet-based fieldbus system, inversection and experiments in automation technology. (www.wikipedia.org)  EtherCAT Device Device using EtherCAT communication  FCS A Frame Check Sequence refers to an error-detecting code added to a frame in a communicate protocol. (www.wikipedia.org)  FMMU The Fieldbus Memory Management Unit belongs to the DLL and can be found in each I/O terr FMMUs are used to map logical addresses bitwise or bytewise to physical addresses of the Eth SubDevice Controller. (Beckhoff Infosys)  FoE File Access over EtherCAT is a mailbox application protocol generally intended to transfer file an EtherCAT network in both directions, and as such it can be used in any state where the mail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | during                                                   |

| and perform the official EtherCAT Conformance Test. (ETG Brochure 11/2018)  The EtherCAT Technology Group is a global organization in which OEM, End Users and Tech Providers join forces to support and promote the further technology development. (www.ethercat The Ethernet for Control Automation Technology is an Ethernet-based fieldbus system, inverse Beckhoff Automation. The protocol is standardized in IEC 61158 and is suitable for both hard are real-time computing requirements in automation technology. (www.wikipedia.org)  EtherCAT Device Device using EtherCAT communication  FCS A Frame Check Sequence refers to an error-detecting code added to a frame in a communicate protocol. (www.wikipedia.org)  FMMU The Fieldbus Memory Management Unit belongs to the DLL and can be found in each I/O terr FMMUs are used to map logical addresses bitwise or bytewise to physical addresses of the Eth SubDevice Controller. (Beckhoff Infosys)  FoE File Access over EtherCAT is a mailbox application protocol generally intended to transfer file an EtherCAT network in both directions, and as such it can be used in any state where the mail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                          |

| Providers join forces to support and promote the further technology development. (www.etherca  The <b>Ether</b> net for <b>C</b> ontrol <b>A</b> utomation <b>T</b> echnology is an Ethernet-based fieldbus system, invented Beckhoff Automation. The protocol is standardized in IEC 61158 and is suitable for both hard are real-time computing requirements in automation technology. (www.wikipedia.org)  EtherCAT Device Device using EtherCAT communication  FCS A <b>F</b> rame <b>C</b> heck <b>S</b> equence refers to an error-detecting code added to a frame in a communicate protocol. (www.wikipedia.org)  FMMU The <b>F</b> ieldbus <b>M</b> emory <b>M</b> anagement <b>U</b> nit belongs to the DLL and can be found in each I/O terror FMMUs are used to map logical addresses bitwise or bytewise to physical addresses of the Eth <b>S</b> ubDevice Controller. (Beckhoff Infosys)  FoE <b>F</b> ile <b>A</b> ccess over <b>E</b> therCAT is a mailbox application protocol generally intended to transfer file an EtherCAT network in both directions, and as such it can be used in any state where the mail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TG                                                       |

| Beckhoff Automation. The protocol is standardized in IEC 61158 and is suitable for both hard ar real-time computing requirements in automation technology. (www.wikipedia.org)  EtherCAT Device Device using EtherCAT communication  FCS A Frame Check Sequence refers to an error-detecting code added to a frame in a communicate protocol. (www.wikipedia.org)  FMMU The Fieldbus Memory Management Unit belongs to the DLL and can be found in each I/O terr FMMUs are used to map logical addresses bitwise or bytewise to physical addresses of the Eth SubDevice Controller. (Beckhoff Infosys)  FoE File Access over EtherCAT is a mailbox application protocol generally intended to transfer file an EtherCAT network in both directions, and as such it can be used in any state where the mail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |

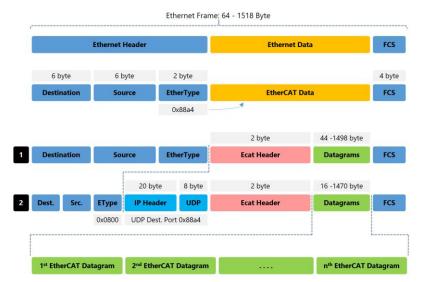

| FCS  A Frame Check Sequence refers to an error-detecting code added to a frame in a communicate protocol. (www.wikipedia.org)  FMMU  The Fieldbus Memory Management Unit belongs to the DLL and can be found in each I/O terr FMMUs are used to map logical addresses bitwise or bytewise to physical addresses of the Eth SubDevice Controller. (Beckhoff Infosys)  FoE  File Access over EtherCAT is a mailbox application protocol generally intended to transfer file an EtherCAT network in both directions, and as such it can be used in any state where the mail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                          |

| FMMU  The Fieldbus Memory Management Unit belongs to the DLL and can be found in each I/O terr FMMUs are used to map logical addresses bitwise or bytewise to physical addresses of the Eth SubDevice Controller. (Beckhoff Infosys)  FoE  File Access over EtherCAT is a mailbox application protocol generally intended to transfer file an EtherCAT network in both directions, and as such it can be used in any state where the mail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |

| FMMUs are used to map logical addresses bitwise or bytewise to physical addresses of the Eth SubDevice Controller. (Beckhoff Infosys)  FoE File Access over EtherCAT is a mailbox application protocol generally intended to transfer file an EtherCAT network in both directions, and as such it can be used in any state where the mail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | tions                                                    |

| an EtherCAT network in both directions, and as such it can be used in any state where the maill                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |

| FPGA A <b>F</b> eld- <b>P</b> rogrammable <b>G</b> ate <b>A</b> rray is an integrated circuit designed to be configured by a custo a designer after manufacturing. (www.wikipedia.org)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | mer or                                                   |

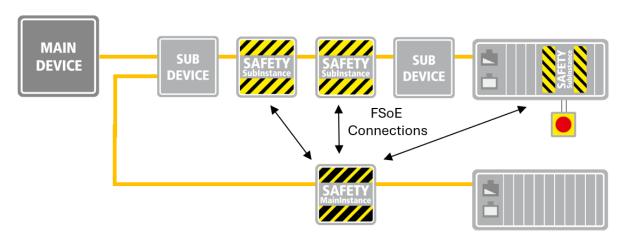

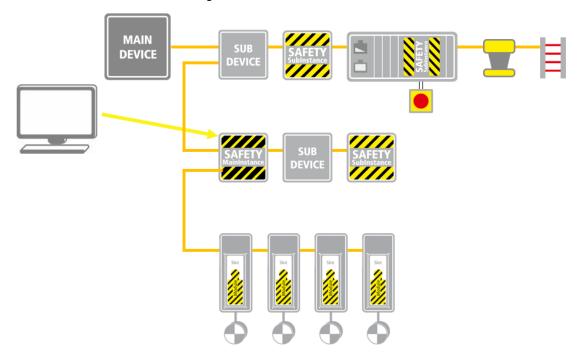

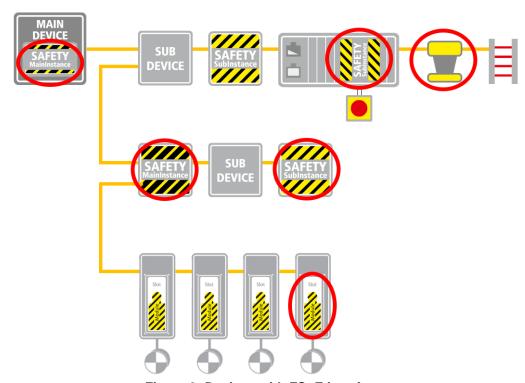

| FSoE EtherCAT utilizes the protocol Safety over EtherCAT ( <b>F</b> ail <b>S</b> afe <b>o</b> ver <b>E</b> therCAT) to transfer safe critical control data through the same medium as the control data themselves. (www.ethercat.or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

| FSoE Device Using EtherCAT communication with FSoE feature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |

| GPIO  A <b>G</b> eneral- <b>P</b> urpose <b>I</b> nput/ <b>O</b> utput is an uncommitted digital signal pin on an integrated circuit of electronic circuit board whose behavior—including whether it acts as input or output—is controll the user at run time. (www.wikipedia.org)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                          |

| HAL  A Hardware Abstraction Layer is an abstraction layer, implemented in software, between the p hardware of a computer and the software that runs on that computer. Its function is to hide differ in hardware from most of the operating system kernel, so that most of the kernel-mode code do need to be changed to run on systems with different hardware. (www.wikipedia.org) r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | rences                                                   |

| Inter-Integrated Circuit is a synchronous, multi-master, multi-slave, packet switched, single-end serial computer bus invented in 1982 by Philips Semiconductor (now NXP Semiconductors). It is widely used for attaching lower-speed peripheral ICs to processors and microcontrollers in short distance, intra-board communication. (www.wikipedia.org)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | S                                                        |

| The Interglobal Electrotechnical Commission is a Swiss association that acts as an interglobal standards organization that prepares and publishes interglobal standards for all electrical, electrical, and related technologies – collectively known as "electrotechnology". (www.wikipedia.org)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                          |

| The International Organization for Standardization is an international standard-setting body core of representatives from various national standards organizations. (www.wikipedia.org)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | mposed                                                   |

| A <b>L</b> ight- <b>E</b> mitting <b>D</b> iode is a semiconductor light source that emits light when current flows throu (www.wikipedia.org)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                          |

| Abbreviations | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LVDS          | Low-Voltage Differential Signaling, also known as TIA/EIA-644, is a technical standard that specifies electrical characteristics of a differential, serial communication protocol. LVDS operates at low power and can run at very high speeds using inexpensive twisted-pair copper cables. LVDS is a physical layer specification only; many data communication standards and applications use it and add a data link layer as defined in the OSI model on top of it. (www.wikipedia.org)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| MCI           | Micro Controller Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

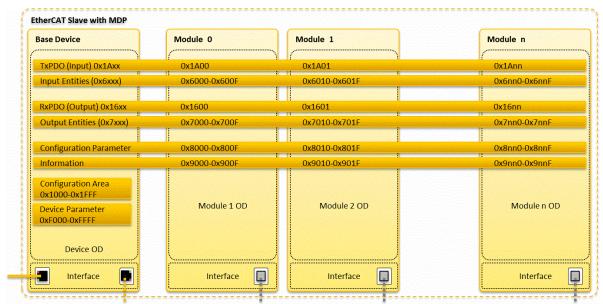

| MDP           | The <b>M</b> odular <b>D</b> evice <b>P</b> rofile defines a modeling of structures within a device. Mainly the object dictionary structure and corresponding behavior of the entries is defined by the MDP. The intention is to provide an easy way for MainDevice and configuration tools to handle the devices. (Knowledge Base)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| MII           | The <b>M</b> edia- <b>I</b> ndependent <b>I</b> nterface was originally defined as a standard interface to connect a Fast Ethernet (i.e., 100 Mbit/s) media access control (MAC) block to a PHY chip. The MII is standardized by IEEE 802.3u and connects different types of PHYs to MACs. Being media independent means that different types of PHY devices for connecting to different media (i.e. twisted pair, fiber optic, etc.) can be used without redesigning or replacing the MAC hardware. Thus any MAC may be used with any PHY, independent of the network signal transmission media. (www.wikipedia.org)                                                                                                                                                                                                                                                                                                                                                     |  |

| NIC           | A <b>N</b> etwork <b>I</b> nterface <b>C</b> ard (also known as a network interface controller, network adapter, LAN adapter or physical network interface) is a computer hardware component that connects a computer to a computer network. (www.wikipedia.org)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| NW            | NetWork                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| OEM           | An <b>O</b> riginal <b>E</b> quipment <b>M</b> anufacturer is a company that produces parts and equipment that may be marketed by another manufacturer. (www.wikipedia.org)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| PD            | Power Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| PDI           | The <b>P</b> hysical <b>D</b> evice <b>I</b> nterface is an interface that allows access to the ESC from the process side. (Beckhoff Infosys)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| PDO           | The <b>P</b> rocess <b>D</b> ata <b>O</b> bject protocol is used to process real time data among various nodes. (www.wikipedia.de)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| PELV          | IEC 61140 defines a <b>P</b> rotective <b>E</b> xtra- <b>L</b> ow <b>V</b> oltage system as "an electrical system in which the voltage cannot exceed ELV under normal conditions, and under single-fault conditions, except earth faults in other circuits". (www.wikipedia.org)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| PhL           | Physical Layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| PIC           | Programmable Integrated Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| PLC           | A Programmable Logic Controller or programmable controller is an industrial digital computer which has been ruggedized and adapted for the control of manufacturing processes, such as assembly lines, or robotic devices, or any activity that requires high reliability control and ease of programming and process fault diagnosis. (www.wikipedia.org)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| PSD           | Power Sourcing Device, s. PSE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| PSE           | Power Sourcing Equipment are devices that provide (source) power on the Ethernet cable. This device may be a network switch, commonly called an endspan (IEEE 802.3af refers to it as endpoint), or an intermediary device between a non-PoE-capable switch and a PoE device, an external PoE injector, called a midspan device. (www.wikipedia.org)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |